Directrices De Diseño De ESD: Para Circuitos Electrónicos - Requisitos, Métodos Y Diseño.

Aunque la utilización de una zona protegida contra ESD es el enfoque correcto para cualquier operación en la que se manipulen componentes y conjuntos electrónicos, sigue siendo necesario garantizar que sean lo más robustos posible como resultado de su diseño.

La aplicación de las directrices de diseño para la protección contra ESD es esencial para cualquier circuito que se conecte con el mundo exterior.

Es frecuente que los equipos tengan conectores para interfaces externas, que son propensos a los efectos de la estática, ya que los equipos pueden utilizarse a menudo en entornos que no están protegidos contra la estática. Es esencial que estén protegidos. Además, si el equipo se diseña de forma robusta, es menos probable que falle.

Requisitos de protección contra la ESD

Dado que los dispositivos electrónicos utilizados en los equipos electrónicos actuales son susceptibles de sufrir descargas electrostáticas, es necesario emplear directrices de diseño de ESD que garanticen que los dispositivos utilizados estarán protegidos contra sus efectos.

Las directrices de diseño de ESD y la protección utilizada son de especial importancia cuando las conexiones se encuentran en la periferia del equipo y pueden ser accesibles por el usuario.

Mira También Qué Son Las Telecomunicaciones Celulares - Desarrollo, Generaciones y Conceptos.

Qué Son Las Telecomunicaciones Celulares - Desarrollo, Generaciones y Conceptos.Al acceder a los puertos externos, los usuarios no tomarán ninguna precaución contra la ESD, si es que siquiera la conocen. Por lo tanto, es necesario proporcionar una protección total para los puertos externos que puedan existir.

Los dispositivos electrónicos que se fabrican hoy en día suelen tener que sobrevivir a una descarga de contacto de 8 kV (es decir, cuando los 8 kV se descargan directamente sobre la clavija a través de un contacto metálico) o a una descarga de aire de 15 kV (cuando el punto de 15 kV está cerca de la clavija y se descarga a través de un espacio de aire).

Aunque este es el objetivo, no todos los dispositivos sobrevivirán a esto y en muchos casos la descarga puede ser mayor que esto. Por lo tanto, es conveniente añadir una protección adicional.

Métodos de diseño de ESD

La clave de las directrices de diseño de ESD para proteger los dispositivos en cualquier línea de entrada/salida (I/O) externa, es evitar que la tensión suba por encima de un nivel que dañe el dispositivo de interfaz.

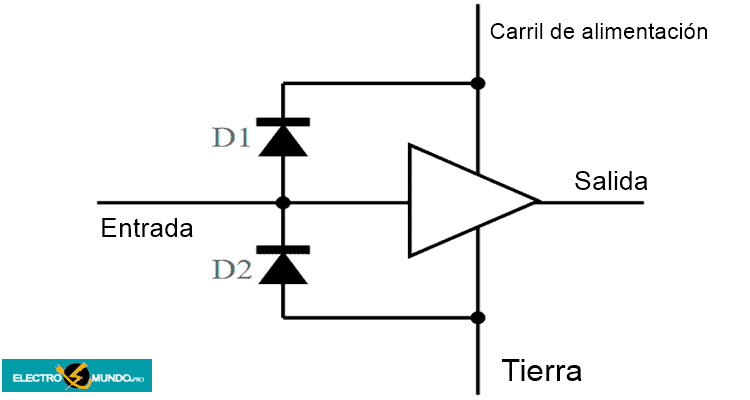

Esto puede lograrse utilizando un circuito que sujete las tensiones máximas justo fuera de los extremos de funcionamiento máximos. Normalmente, esto puede ser justo por encima de la tensión del carril y justo por debajo de la línea de cero voltios.

Mira También ¿Qué es el 2G GSM? - Servicios Y Conceptos Básicos

¿Qué es el 2G GSM? - Servicios Y Conceptos BásicosUn circuito típico que puede utilizarse para sujetar las tensiones emplea diodos de polarización inversa desde la línea de entrada hasta el carril de tensión y hasta tierra. Este circuito de protección ESD debe garantizar que las excursiones de tensión en la línea de entrada sean limitadas.

Los diodos también deben tener un bajo nivel de corriente residual, y la capacitancia debe ser baja para asegurar que la respuesta de frecuencia / tasa de datos y otros parámetros de entrada no se vean afectados.

El funcionamiento del circuito es muy sencillo, ya que los diodos D1 y D2 tienen polarización inversa en condiciones normales de funcionamiento. Sin embargo, si se produce un impulso que eleve la tensión de entrada por encima de la tensión del carril, el diodo superior, D1, se conducirá.

Del mismo modo, si la tensión cae por debajo de la tensión de tierra, el otro diodo, D2, conducirá. Utilizando diodos de señal ordinarios, las máximas excursiones de tensión que podrían esperarse en la línea de entrada en el primer análisis pueden ser de +0,5V por encima del carril y -0,5V por debajo de tierra. Sin embargo, este no es siempre el caso, como se ve a continuación.

La curva de respuesta típica para una descarga electrostática está definida por la norma IEC61000-4-5 y simula una curva típica de descarga electrostática. La forma de onda tiene un tiempo de subida de aproximadamente 1 ns y el nivel de corriente alcanza un máximo de 30A.

Mira También Que Es IS-95, cdmaOne Y Cual Es Su Historia.

Que Es IS-95, cdmaOne Y Cual Es Su Historia.Para suprimir estas tensiones, se necesitan circuitos de sujeción muy eficaces y las directrices de diseño de las descargas electrostáticas deben especificar los componentes aceptables y los límites de rendimiento.

Para proporcionar una aproximación a la tensión de apriete de un diodo, la tensión de apriete puede aproximarse como sigue:

Vclamp = Vconducción + (Rdynamic x corriente)

Se puede observar que la tensión de bloqueo está relacionada tanto con la tensión de conducción o de ruptura (dependiendo del tipo de diodo utilizado) como con la resistencia dinámica del diodo.

Con las corrientes instantáneas muy elevadas que presentan las descargas electrostáticas, incluso valores muy bajos de inductancia harán que la resistencia dinámica sea lo suficientemente alta como para que aparezcan tensiones excesivas en las líneas de interfaz.

Mira También Que Es Y Como Funciona CDMA2000 1X / 1XRTT - Todo Lo Que Necesitas Saber

Que Es Y Como Funciona CDMA2000 1X / 1XRTT - Todo Lo Que Necesitas SaberIncluso con tensiones de pinza de CC de unos 5 V y diodos de conmutación rápida, las tensiones que aparecen en los terminales del dispositivo a causa de una descarga electrostática pueden superar los 100 V. El circuito de sujeción habrá limitado la descarga, pero no en la medida prevista. En muchos casos esto será suficiente debido a la corta duración de los pulsos, y los circuitos pueden sobrevivir

Por lo tanto, es necesario optimizar el circuito para proporcionar el nivel de protección requerido.

Diseño de placas de circuito impreso para ESD

Además de diseñar correctamente el circuito en sí para la supresión de ESD, el diseño y la disposición de la placa de circuito impreso también es muy importante. El esfuerzo invertido en garantizar que el diseño de la placa de circuito impreso cumpla los requisitos de supresión de ESD ahorrará costosas depuraciones posteriores y también mejorará la fiabilidad general del equipo final, ya que los problemas de ESD se manifestarán menos.

Existen algunas directrices básicas de diseño para garantizar que cualquier diseño de placa de circuito impreso, PCB, sea capaz de reducir al mínimo los problemas derivados de la ESD:

- Eliminar los bucles del circuito: Los bucles en una línea pueden dar lugar a corrientes no deseadas derivadas de la inducción. Si bien esto degradará el rendimiento por la captación general no deseada, también es importante para la protección contra la ESD porque se pueden inducir picos de corriente no deseados (y, por tanto, tensiones) en cualquier bucle. Hay que asegurarse de que no existan bucles.

- Utilizar capas de plano de tierra en la placa de circuito impreso: Una forma de reducir los bucles de tierra es utilizar un plano de tierra dentro de la placa de circuito impreso. De este modo, las señales se conectarán a tierra de forma eficaz y se reducirá la posibilidad de que se produzcan bucles de tierra.

- Reduzca la longitud de las líneas: Cualquier cable actuará como una antena. Con los tiempos de subida muy cortos que presentan los pulsos de ESD, cualquier antena tiene la capacidad de recibir picos de alto voltaje. Al reducir las longitudes de las líneas, se reducirá el nivel de energía radiada que se recibe y los picos resultantes de las descargas electrostáticas serán menores.

- Reduzca la inductancia parásita alrededor de los circuitos de protección: Muchos circuitos electrónicos incorporan circuitos de protección ESD. Éstos sólo pueden ser eficaces si los niveles de inductancia parásita son bajos. La inductancia parásita derivada del diseño de la placa de circuito impreso puede reducirse manteniendo las longitudes de las líneas en esta zona especialmente cortas, así como aumentando la anchura de las pistas.

- Evite colocar las pistas sensibles cerca de los extremos de la placa de circuito impreso: Dado que los niveles de captación de descargas estáticas suelen ser mayores cerca de los extremos de la placa, es aconsejable mantener las líneas sensibles alejadas de estas zonas. Las líneas de entrada y salida a menudo tendrán que llegar al borde de la placa de circuito impreso en algún momento, pero se pueden alejar del borde tan pronto como sea posible.

Asegurarse de que un conjunto electrónico está protegido contra los efectos de la ESD es esencial para cualquier elemento en el que se puedan realizar conexiones externas. Al proteger una unidad de esta manera, también se podrá presentar para la certificación y el marcado.

Por ejemplo, el marcado CE, que puede ser necesario para su venta en el mercado abierto. Para que un producto sea resistente a la ESD, los requisitos deben aplicarse en las primeras fases del diseño. Las modificaciones necesarias en una fase tardía del diseño serán difíciles y costosas de aplicar.

Deja una respuesta

►TAMBIÉN DEBERÍAS LEER...